Research

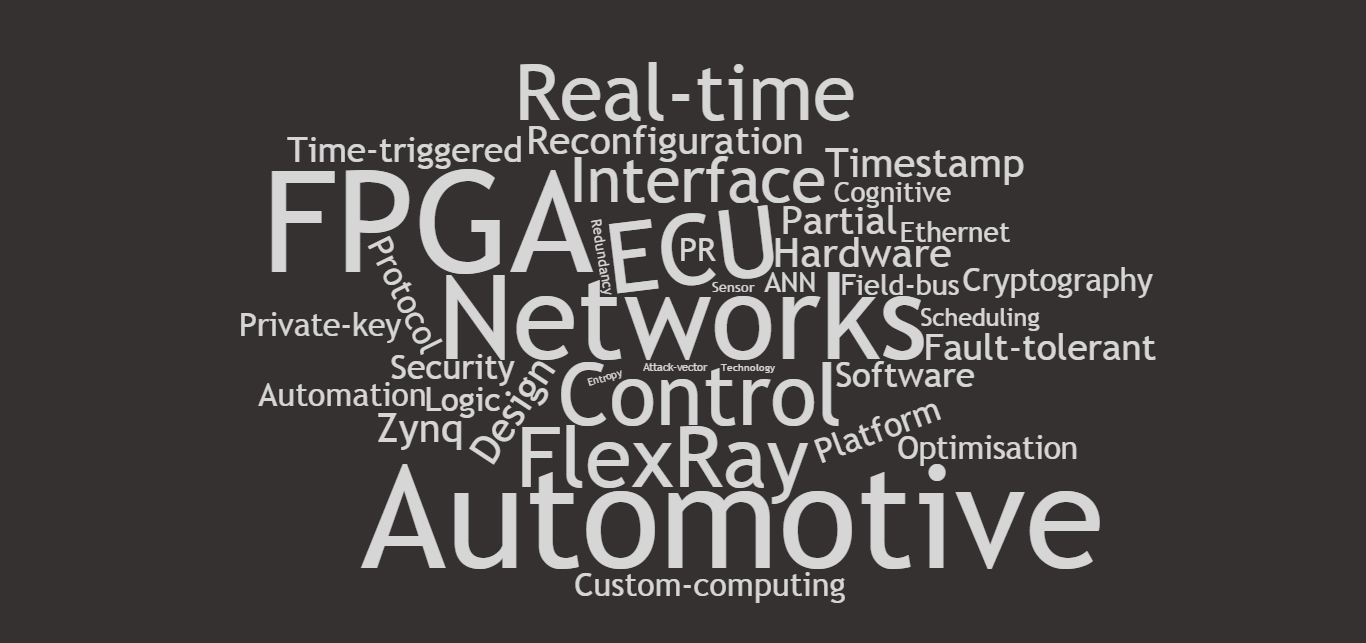

My research area focuses on building computer architectures that enable unique ways for improving compute efficiency, network performance and provide reactive capabilities to adapt to changing environments, through seamless interaction of software and hardware. I have applied this approach to tailor compute/network architectures in different domains such as automotive embedded systems, cognitive radio systems and internet of things. A key enabler for his research is fully programmable platforms (or reconfigurable hardware), which enables both the software and the underlying hardware to be adapted to the compute requirements and specifications, either statically (i.e., at design time) or dynamically (i.e., at run-time).

Our current research focus is on enabling sustainable, adaptable and energy-efficient accelerators/digital designs for a range of data-driven tasks such as (light-weight) deep learning, media/video processing, communication networks and high-performance computing, among others. We investigate novel integration approaches, algorithmic and compiler optimisations and design space exploration schemes for co-designing and co-optimising applications with their accelerators.